In my last post, I explained the importance of JESD204B subclasses and reviewed the details of subclass 0 and 1. Today, I’ll explore subclass 2.

Subclass 2

Subclass 2 analog-to-digital converters (ADCs) and digital-to-analog converters (DACs) have a local multi-frame clock (LMFC) similar to subclass 1. The devices use LMFC to establish a timing reference and alignment point. In subclass 2, the logic device LMFC will always act as the master LMFC reference point, and any attached ADCs and DACs will re-align their LMFC to match the LMFC within the logic device.

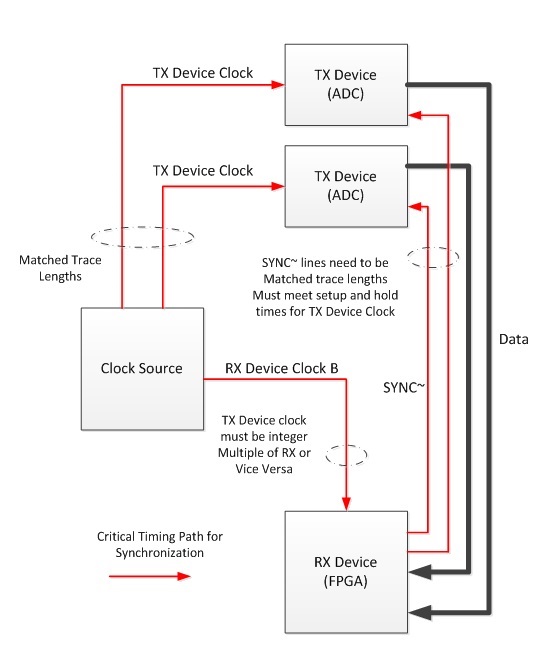

In general, the SYNC signal is aligned to the LMFC and communicates a request to start code group synchronization (CGS). It also indicates the LMFC position. The SYNC signal in this case is critical, and you must route this signal with some care to ensure it meets the sample and hold times of the device clock. For multiple data converters connected to a logic device, all of the device clocks and SYNCs must be skew matched to achieve device synchronization.

If you need to connect an ADC to the logic device, the RX logic device will drive SYNC low to start CGS. This SYNC signal going high will establish the LMFC edge within the ADC. For multiple ADCs connected to a logic device, the SYNC signal to each ADC must be trace-length matched to ensure you establish the same LMFC in each ADC, resulting in the same deterministic latency. This ensures that the multiple devices are synchronized. Figure 1 shows the timing connections for an ADC connection to the logic device.

Figure 1 – ADC connections for subclass 2

When you need to connect a DAC to the logic device, the DAC will be the RX device. The DAC RX device will drive SYNC low to the TX logic device to start CGS. It also tells the logic device where the DAC LMFC is relative to the logic device LMFC.

Since the logic device acts as the master LMFC reference, it will send back configuration messages in the second frame of the initial lane alignment sequence (ILAS) multi-frame to indicate if the DAC LMFC requires adjustment. The TX logic device will send back the following parameters to the DAC:

PHADJ - is a 1-bit signal that indicates if you need to adjust the DAC’s LMFC

ADJCNT - is the number of resolution steps needed to adjust the DAC’s LMFC (TX logic device must know the adjustment resolution of the DAC)

ADJDIR - is the direction of the phase adjustment – 0 advance, 1 delay

The DAC will receive these messages in the ILAS configuration multi-frame and adjust its LMFC accordingly before toggling SYNC again. This will send another CGS request to the TX logic device to see if the adjusted LMFC is aligned. This process will continue until ADJCNT=0. This should ensure alignment between the LMFCs of the DAC and TX logic device.

With the LMFC aligned, you can achieve deterministic latency between the DAC and the TX logic device. If you achieve the same deterministic latency on multiple DACs, you will achieve multiple device synchronization. Figure 2 shows the timing connections required for subclass 2 with multiple DACs.

Figure 2 – DAC connections for subclass 2

The standard recommends that designers not use subclass 2 above 500 Msps, but instead use subclass 1. As opposed to the SYSREF signal used in subclass 1, which is source synchronous with the device clock from the same clock chip, the SYNC signal is system synchronous. As a result, it is more difficult to meet setup and hold times at higher sampling rates.

Summary

You must understand the three JESD204B subclasses and their implementation differences before deciding which subclass to use. For applications that require backwards compatibility to JESD204A, which has no provisions for deterministic latency, subclass 0 is the best choice. For applications that require deterministic latency or multi-device synchronization, either subclass 1 or subclass 2 can be used, with the caveat that subclass 2 should not be used above 500 Msps.

Stay tuned for next month’s blog, where I’ll discuss the process of verifying deterministic latency between an ADC and the logic device.

Additional resources:

- Take a deeper dive into JESD204B subclasses and deterministic latency in this training presentation.

- Download our JESD204B white paper for tips on what you need to know when transitioning to JESD204B.

- Read more JESD204B blogs.

- Learn about TI’s JESD204B ADCs, DACs, clocks and tools.