As a former college instructor who regularly lulled his students to sleep with a traditional lecture format, I’m excited to announce that TI is offering a “Hands-OnAnalog Basics” workshop at Design West 2013(April 22-25 in San Jose, Calif.)with our very ownamplifier expert, Art Kay! This workshop is ideal for all analog engineers – from beginners to veterans – as well as digital designers and new college graduates. Op amp topics from bandwidth to noise will be discussed, simulated, calculated, demonstrated andmeasured!

Everyone who attends the session will have their own workstation composed of a computer, National Instruments (NI) myDAQ, and multiple custom Texas Instruments (TI) experimenter boards. Below is a picture of the hardware setup we’ll use to demonstrate common-mode voltage, output swing, slew rate and bandwidth during the session.

This hardware will correlate real-world results with theory and simulation. The results from our output swing module are shown below. Believe it or not, these results even correspond to the data sheet specifications!

TINA-TI Simulation Measured Results

Each topic will start with approximately 15-20 minutes of theory (hopefully not enough to lull everyone into a deep slumber) before transitioning to interactive activities like running TINA-TI simulations and taking real-world data using the NI myDAQ. In contrast to my higher-education days, this methodology transforms the experience from passive to active participation, which will increase comprehension and retention of the concepts presented.

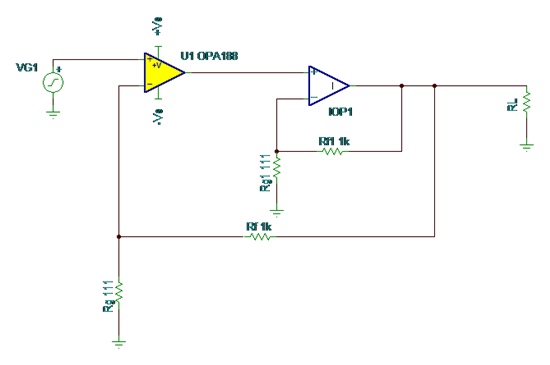

In addition to the aforementioned topics (bandwidth, noise, slew rate, common-mode voltage, and output swing), there are also modules that discuss active filtering and op amp stability. The filtering module compares the Sallen-Key and multiple-feedback (MFB) topologies and shows the consequences of not selecting the right op amp. The stability module shows you how to stabilize an op amp driving a 1uF load using an isolation resistor with and without dual feedback. The selection of the topics was based on decades of experience supporting the design community, so the session should be very informative!

While I’m unable to be there in person, I helped Art develop this workshop and am thrilled to offer it at Design West 2013. I hope everyone who attends the session will find it to be rewarding, useful and fun!

Be sure you’re registered for Design West in San Jose, and then plan to attend one of our three “Hands on Analog Basics: Beginner Knowledge and Veteran Refresher” sessions in the Low-Power Design track: Monday morning (full session), Thursday morning (part 1) or Thursday afternoon (part 2).

Some browsers may experience compatibility issues when accessing information from the above links. If you’re not able to access thelinks, consider updating your browser or your version of Flash.