- Learn more about TI’s broad current-sense portfolio.

- Watch this video on “Current Sensing: Low Side, High Side and Zero Drift.”

- Online training: Getting started with current sense amplifiers

- Check out these related TI Designs reference designs:

How to get started with current sense amplifiers – part 1

Multi-dimensional inductive sensing

The title of this blog sounds like an excerpt from a science fiction movie, but in reality, integrating multiple sensor analog front-ends (AFEs) into a single device is nothing new. Suppliers have been releasing duals and quads of just about every building block, analog-to-digital converter (ADC) or digital-to-analog converter (DAC) since the integrated circuit became a mainstream product.

But what about industrial applications such as inductive sensing? (For those of you not familiar with inductive sensing, check out my article in Electronic Design, “Redefining Inductive Sensing.”) It turns out that inductive sensing has been around since the late 1950s, but the idea of integrating the entire AFE into a single device was a Texas Instruments first.

If one channel is good, then adding more channels and increasing the resolution is even better. Many applications such as multiaxis position sensing or copier-paper-path-jam detection require more than one channel. A great automotive application is measuring brake pads. For cars, this is currently limited to high-end luxury vehicles; but for commercial trucks, it’s a necessity, often monitored by onboard computers to alert both the driver and service personnel that there may be a problem. If the brake pad gets excessively worn, the truck’s brakes can fail in a panic stop.

At minimum, you’d need four channels per axle. This is done by placing a sensing coil in the middle of the brake piston, spaced from the disk (see Figure 1). Pads can be engineered to either be transparent to the alternating current (AC) field or have a strategic hole cut for the sensing coil to “see” through. As the pads wear, the coil moves closer to the disk, and this determines how much of the pad remains.

Figure 1: Example of using multiple channels of inductive sensing to measure brake-pad wear

Another application exists in low-cost 3D printers. In many robotic and heavy-duty applications, linear variable differential transformers (LVDTs) are used to sense linear position, but for low-cost 3D printers, this can be too expensive. Another way to sense linear position is with an asymmetrical (or stretched) coil etched directly onto a printed circuit board (PCB) and a simple rectangular target. This method shapes the AC magnetic field along the length of the coil, allowing the inductive sensing AFE to detect position extremely accurately – and very inexpensively. (For more information on this method, see this application note.)

Using an LDC1614 multichannel inductance-to-digital converter (LDC) with this method can provide four degrees of freedom – plenty for a low-cost appliance such as a desktop 3D printer.

So when you need to sense distance or position very accurately for either multiple dimensions or simply multiple channels, take a look at the newest series of LDCs from TI. The applications are endless and limited only by your imagination.

Additional resources

- Learn more about inductive sensing.

- Read other blog posts about designing with LDCs.

- Start a multichannel LDC design with WEBENCH® Inductive Sensing Designer.

- See how LDCs work in the Touch on Metal Buttons with Integrated Haptic Feedback Reference Design.

How to get started with current sense amplifiers – part 2

In part 1 of this series, I discussed the concepts of low-side or high-side monitoring and current flow directionality. In this second installment, I will discuss “how” the current information is used.

What do I mean when I say “how”? A current-sense amplifier measures the current value, and in some cases can also calculate the power. In some cases, the amplifier can compare the current value to a threshold, but it cannot make a decision about what the value means and what the system should do about it.

The output of a current-sense amplifier typically has one of three uses in the signal-conditioning chain, listed below.

- The output can act as feedback to control a specific action of the next portion of the circuit.

- It can go into a system microcontroller (MCU) that will make systemwide decisions based on the current level.

- It can act as an interrupt to notify a controller that a specific threshold has been exceeded, without the controller caring about the actual value.

The first use of a current-sense amplifier output is leveraging the current level as feedback into other portions of the circuit, as shown in figure 1. In this case, an analog output device such as the INA210 or INA282 will most likely offer the best type of solution. The voltage output feeds into the input pin of the device that needs the feedback. An example of this is regulating a light-emitting diode (LED) with a constant current regulator. The current fed into the LED is measured with a current-sense amplifier, and that output goes into the feedback pin of the regulator, such as the TPS54218, a 2.95-V-to-6-V-input, 2-A synchronous step-down SWIFT™ converter.

Figure 1: Current-level output gives feedback to control an action in other parts of the circuit

The second and most common use case is to provide the current level information to a controller that will then control other aspects of the system based on the level, as shown in figure 2. For example, the current system’s current level may be used to adjust fan speed to match the required cooling to the heat being created. The current level can also adjust the clock speed, at which a high-performance integrated circuit (IC) is operating to balance the performance versus the heat.

While the analog output devices referenced above may offer all of the performance needed for this use case, there needs to be an analog-to-digital converter (ADC) for the controller to use the data. Many MCUs offer integrated ADCs that can do this job. However, using a digital-output device such as the INA226 or INA230 may allow the use of a lower cost MCU or free up the integrated ADC to perform other functions. In addition, many of these newer digital-output devices offer an alert functionality that can allow the MCU to ignore the current measurement system until a certain threshold is reached. Once the alert triggers the MCU, it then starts monitoring the current to determine the next steps.

Figure 2: Current level feeds into an MCU, which controls other aspects of the system

This brings us to the third common use case: simple alerts that trigger when an overcurrent threshold is exceeded, as shown in figure 3. (Think eFUSE technology.) A device like the INA300 is a simple-to-implement, small-footprint, low-cost, overcurrent comparator that supports this type of alert-only use case.

Figure 3: Current level serves as an interrupt, notifying a controller that a specific threshold has been exceeded

I hope you now understand the three main ways that current information is used in current-sense amplifiers. In the next installment, I’ll discuss how the current range affects device-selection criteria and basics on calculating the value of the shunt resistor needed.

Additional resources

- Learn more about TI’s broad current-sense amplifier portfolio.

- Watch this video about how the INA300 is optimizing overcurrent detection.

- Check out these related TI Designs reference designs:

What are you sensing? Re-thinking system efficiency and reliability - part 1

If you ask an engineer if they would like an efficient and reliable system, the answer will of course be yes. What that definition of efficiency and reliability is – and what it ultimately takes to get the system there – is not nearly as easy to answer.

In looking at reliability, a common place to start is to determine what level of protection will ensure that the system will be protected if any unintended operating conditions occur. Obviously, a fuse is an easy implementation to protect against a shorted condition for an overcurrent protection scheme. But then you have to worry about how to get that system back into the field after a fuse blows following a shorted condition. Operational downtime is expensive and, in many cases, unacceptable. The fuse only offers two pieces of information: whether or not the current is excessively high, and whether or not the system power bus has been opened.

A circuit that actively measures the system current can very precisely detect if an out-of-range condition exists and allow operating performance adjustments to enable safe operation up to the full power budget without sacrificing reliability.

The INA199 current-shunt monitor is a common building block for this function due to its small printed circuit board (PCB) footprint and accuracy, as well as its integrated, matched gain-setting resistors. The output is directed to a comparator with a fixed threshold corresponding to the current level the functional block is looking to detect, as shown in Figure 1.

Figure 1: INA199 current-shunt monitor in a typical application

The comparator output can directly control circuitry to open the power-supply bus, or allow a microcontroller to either throttle the system performance and continue operation within the allowable power budget or shut the system down altogether. For critical faults, this shutdown capability is extremely important to prevent the out-of-range condition from damaging system components.

The current-limit threshold for this circuit is set by the reference voltage applied to the noninverting input of the comparator. This voltage level directly corresponds to the current level measured by the INA199. Using a voltage divider, you can calculate the reference voltage with Equation 1:

Limit reference voltage = current limit (A) * shunt resistor (Ω) * amplifier gain (V/V) (1)

The INA300 is a specialized current-sensing comparator that approaches this same function a little differently by integrating the current-sense amplifier and comparator into one device. Figure 2 shows this comparator in a typical application. The approach is the same as the previous example using the INA199, in that the INA300 has a threshold limit set using a single external resistor that corresponds to the current limit for the system.

Figure 2: INA300 current-sensing comparator block diagram

An internal 20µA current source is present at the limit pin that creates a reference voltage for the comparator based on the value of the RLIMIT resistor connected to that pin. This voltage is set to equal the voltage developed across the shunt resistor at the current-limit level. Equation 2 calculates the RLIMIT resistor value:

I hope you are now familiar with how the INA199 and INA300 devices enable more effective detection and handling of overcurrent events. Stay tuned for the next part of my series, where I will discuss other ways system designers can take advantage of dedicated overcurrent detection. How do you define reliability and efficiency? Comment below to share your answer.

Additional resources

- Learn more about TI’s current-sense portfolio.

- Watch this video about how the INA300 is optimizing overcurrent detection.

- Online training: Getting started with current-sense amplifiers.

- Check out these related TI Designs reference designs:

Get Connected: High-speed LVDS comparator

Welcome back to the Get Connected blog series on Analog Wire. In my previous post, I discussed how you can use low-voltage differential signaling (LVDS) to extend the reach of your serial peripheral interface (SPI) communication bus. In this post, I’ll look at using an LVDS receiver as a high-speed comparator, which can be useful in applications where the output from the crystal oscillator is not optimal, or in a photo-detector circuit in a factory setting.

In applications that require a clock to be distributed across a backplane, cable assembly, or even a complex or large motherboard, the clock edges will suffer from the degrading effects of the medium. The product of these effects may be a clock that looks more like a sine wave than a square wave. The impaired clock may be unusable at this point to the end device, meaning that additional internal design team meetings and board spins are soon to follow.

A simple workaround for this problem is to configure an LVDS receiver as a high-speed comparator by placing a static common-mode voltage on one of the inputs and driving the impaired signal into the opposite input. The product of this LVDS implementation is a cleaned-up clock that swings full rail and can now be distributed to the end devices. Figure 1 depicts the LVDS circuit design, while Figure 2 shows the output of the SN65LVDS4 at 50 MHz. The B input is tied to a static 50 mV, and the A input swings from 0 to 100 mV.

Figure 1: Using an LVDS receiver to improve oscillator edges

Figure 1: Using an LVDS receiver to improve oscillator edges

Figure 2: SN65LVDS4 output at 50 MHz

Another application where an LVDS receiver can be used as a high-speed comparator is in an infrared light photo-detector circuit. A photo diode is reverse-biased, and the leakage current through the diode differs based on whether there is light present (IL) or not present (ID) on the diode. Figure 3 shows an example of this LVDS circuit design.

Figure 3: Photo-detector circuit design using an LVDS receiver

For this example, let’s say that IL is 30 µA and ID is 5 nA. If the R3 value is 100 kΩ, you can use the always faithful Ohm’s law to calculate the high- and low-level voltage as 3 V and 500 mV, respectively. The reference voltage on the B input of the receiver is VCC/2. When the light is blocked, you will have a dark (ID) situation, and a low level will be registered out of the SN65LVDS4 receiver’s R pin. When the light is not blocked, there is a light (IL) situation, and a high level will be registered out of the SN65LVDS4 receiver’s R pin. A circuit like this may be useful in a factory setting where cans or bottles are flying by a sensor in a bottling plant, and a simple counter is needed to measure productivity.

In my next post, I’ll discuss how a multipoint LVDS (MLVDS) device with extended electrostatic discharge (ESD) performance will help you meet the International Electrotechnical Commission (IEC) 61000-4-2 specification. Leave a comment below if you’d like to hear more about anything discussed in this post, or if there is an interface topic you'd like to see in the future.

Clamp diodes: A one-way street

“Am I allowed to have an input signal when VCC = 0 V?”

“What happens if the input or output voltage goes below GND?”

Customers ask these questions quite frequently – and for good reasons. Many standard logic datasheets don’t specify explicitly if conditions are allowed where inputs go above VCC or below ground (GND). The devices themselves have few (if any) performance characteristics in the datasheet at those fringe voltages.

One of the most important features of most TI devices is the presence of electrostatic discharge (ESD) protection. In fact, in some devices, ESD protection circuitry takes up most of the space on the die. Typically, an ESD circuit includes a diode that channels excess current to GND (through reverse breakdown) or VCC (through forward biasing) when the input voltage approaches unsafe levels. The intent is to protect against damaging conditions in the internal circuitry.

However, the ESD diodes can have some unintended effects. For example, if there is an input diode going from the input to VCC, an input voltage at VCC = 0 will cause current to flow through the device to the VCC pin. Likewise, a diode from GND to the input will cause current to flow from GND to the input when the input reaches a certain level below GND.

So how do we know when the input diodes are present, and how can we protect against negative effects?

The absolute maximum ratings table (Table 1) holds the answers.

Table 1: Sample Absolute Maximum Ratings Table

Table 1: Sample Absolute Maximum Ratings Table

On this analog switch, we can see that a voltage on the I/O pins is not allowed to be higher than VCC, or less than -0.5V. Therefore, we can conclude that there is a diode to VCC and a diode from GND on each I/O port of the device.

Figure 1: ESD diode structure of device with Absolute Max Table similar to Table 1

Table 2 offers another example where the absolute maximum rating is structured a bit differently.

Table 2: Sample Absolute Maximum Ratings table with different limits on inputs vs. outputs

Table 2: Sample Absolute Maximum Ratings table with different limits on inputs vs. outputs

We can see here that the diode is present from GND to both the input and output, and the ESD diode to VCC is present at the output. When the device is in a high or low state, there is a risk of conducting current through the VCC diode. This device has a special feature called a high-impedance state that prevents current backflow through the diode. It also has protection circuitry for when VCC = 0, called IOFF.

However, from the VCC + 0.5V statement, we know there is a diode going from the output to VCC, and there is protection circuitry to prevent issues in certain configurations.

Figure 2: ESD diode structure for device with Absolute Maximum Ratings similar to Table 2

But what are the limits? The specs IIK and IOK describe the current limits into the device (positive values) and out of the device (negative values) through ESD diodes. Consider the first case (Table 3), where we had two GND diodes.

Table 3: Sample Ratings for Clamp Currents in Absolute Maximum Ratings

Table 3: Sample Ratings for Clamp Currents in Absolute Maximum Ratings

The current in the GND diode is limited to 50mA. For the second case with the VCC diode, the “output clamp current” would have a +/- symbol, indicating that current can flow in both directions (into the VCC diode or out of the GND diode).

It is best to avoid situations where ESD diodes can turn on. Most data sheets specify an exception to the input and output voltage rules – so if you limit the diode clamp current with a series resistor on the input or output, your device will be at much less risk of damage.

Learn more on designing with standard logic from the following application notes:

- “Latch Up, ESD and Other Phenomena”

- “Understanding and Interpreting Standard-Logic Datasheets”

- “Voltage Translation Between 3.3-V, 2.5-V, 1.8-V and 1.5-V Logic Standards”

Differential pairs: four things you need to know about vias

In a high-speed printed circuit board (PCB), a via is notorious for degrading signal-integrity performance. However, using via structures is unavoidable. In a typical board, components are placed on the top, while differential pairs are routed in inner layers where they lower electromagnetic radiation and pair-to-pair crosstalk. Vias must be used to connect components on the board’s surface to the inner layers.

Fortunately, it’s possible to design a transparent via that minimizes performance impact. In this post, I’ll discuss the following:

- Basic elements of vias

- Electrical properties of vias

- A method to build a transparent via

- Test results of a differential via structure

1. Basics of a via structure

Let’s start by examining the elements of a simple via that connects a top trace to an inner trace. Figure 1 is a 3-D diagram showing a via construction. There are four basic elements: the signal via, via stub, via pad and anti-pad.

Vias are metal cylinders that plate through holes between the top and bottom layers of a board. Signal vias connect traces at different layers. Via stubs are the unused part of the via. Via pads are donut-shaped pads that connect the vias to the top or the inner traces. Anti-pads are the circular clearances in each power or ground layer that prevent electrical short to the plane.

Figure 1: 3-D diagram of a single via

2. Electrical properties of via elements

Let’s walk down the signal path to visualize the electrical property of each via element, shown in Table 1.

Table 1: Electrical properties of the via elements shown in Figure 1

A simple via is a series of π-networks made of capacitance-inductance-capacitance (C-L-C) elements formed within two adjacent layers. Table 2 shows the effect of the via dimensions.

Table 2: Intuitive effect of via dimensions

By balancing the amount of inductance and parasitic capacitance, it’s possible to construct a via with the same characteristic impedance as the trace, thus becoming transparent. There’s no simple equation that translates via dimensions into the C and L elements. A 3-D electromagnetic (EM) field solver can predict the impedance of a structure based on the dimensions used in a PCB layout. By repeatedly adjusting the structure’s dimensions and running 3-D simulations, it’s possible to optimize the via dimension to achieve the desired impedance and bandwidth requirements.

3. Building a transparent differential via

As discussed in my previous post, a differential pair must be implemented with a high degree of symmetry between the A and B wires. The pairs are routed in the same layers, and if there’s a need for a via, it must be implemented in both wires at locations close by. Because the two vias of the differential pair are in close proximity, instead of using two separate anti-pads, an oval anti-pad shared by the two vias reduces parasitic capacitance. A ground via is also placed next to each via so that they provide ground-return paths for the A and B vias.

Figure 2 shows a ground-signal-signal-ground (GSSG) differential via structure example. The distance between the two adjacent vias is called a via pitch. A smaller via pitch introduces more mutual coupling capacitance.

Figure 2: A GSSG differential via with back-drill

Don’t forget that the via stub produces severe degradation to high-speed signal integrity at above 10Gbps. Fortunately, there’s a back-drill PCB manufacturing process that precisely drills through the unused via cylinder.Determined by the manufacturing process tolerance, back-drilling removes the unused via metal and minimizes the via stub to less than 10mils.

A 3-D EM simulator is used to design a differential via with the desired impedance and bandwidth. This is an iterative process that repeatedly adjusts the via dimensions and runs EM simulations until achieving the desired impedance and bandwidth.

4. How to verify performance

The differential via design shown in Figure 2 was built and tested. The test sample consists of a pair of differential traces at the top layer, followed by a differential via to the inner traces, then a second differential via connects to the BGA landing pads at the top layer again. The total length of the signal path is about 1,330mils. I measured its differential impedance with a differential time-domain reflectometer (TDR), its bandwidth by using a network analyzer, and its effect on the signal by measuring the data-eye opening with a high-speed oscilloscope. Figures 3, 4 and 5 show the impedance, bandwidth and eye diagrams, respectively. The left-side plots are the test results with back-drilling, while the right-side plots are those without back-drilling. From the bandwidth plot in Figure 5, it’s clear that back-drilling is necessary to achieve high performance at data greater than 10Gbps.

With back-drill, ZDIFF is about 85Ω Without back-drill, ZDIFF is about 58Ω

Figure 3: TDR impedance plots

Insertion loss at 12.5GHz is about 3dB Insertion loss at 12.5GHz is more than 8dB

Figure 4: Frequency responses

With back-drill, data eye is open Without back-drill, data eye is closed

Figure 5: Data-eye diagrams at 25Gbps

TI has a rich portfolio of high-speed signal-conditioning integrated circuits (ICs) such as retimers and redrivers. They help mitigate imperfections and high insertion loss from all types of differential pairs, enabling reliable data communication and extending transmission distance for modern systems.

Leave a note below – I’d love to hear your feedback on this post or anything you’d like to learn in future “differential pairs” posts.

Additional resources

- See an overview of TI’s portfolio of low-voltage differential signaling (LVDS), multipoint LVDS (MLVDS), signal-conditioning retimers and redrivers.

- Learn more about differential signaling with the LVDS owner’s manual.

- Find out about TI’s two-port 40 Gigabit Ethernet (40GbE)/10GbE quad small form-factor pluggable (QSFP+) signal conditioner reference design.

- Learn about TI’s Peripheral Component Interconnect Express (PCIe) Gen-3 cards with this DS80PCI810 linear redriver reference design.

- Read more about the WEBENCH® Interface Designer tool, which helps designers use TI signal-conditioning ICs to solve differential pairs’ impairments.

Is your op amp filter ringing? Look at Q!

How do you anticipate ringing in the active analog filter of your operational amplifier (op amp)? The purpose of analog filters is to remove signal in an intentional frequency band, not to inadvertently add additional ringing into the signal path. Consider looking at the value of Q, or quality factor, of each filter stage. Figure 1 shows an example of the characteristics of a second-order low-pass Butterworth filter.

Figure 1: Sallen-key, 6kHz low-pass filter using the WEBENCH® Filter Designer tool

The header in Figure 1 provides filter topology, gain, cut-off frequency, Q and the minimum op amp bandwidth, in this case for the OPA124 precision op amp.

These are all valuable entities when designing your filter, but let’s consider the Q in Figure 1, which is equal to 0.864. The value of Q is primarily dependent on the resistor and capacitor values in the circuit and relatively independent of the amplifier. This value of Q indicates that this system is underdamped. This unit-less variable actually quantifies the quality and amount of decay in the system. Q is related to ζ, the damping factor, by Q = 1/(2ζ). Each stage in multi-order filters generates its own Q factor.

If the maximum Q is less than 0.5, the system is overdamped. This type of system output does not ring at all. When the output voltage is displaced from its steady state, the filter’s output returns to its steady state with an exponential decay.

A Q value equal to 0.5 indicates that the system is critically damped. If you are designing a low- or high-pass filter, the first-order filters are the only filters that have a Q this low.

An underdamped circumstance occurs if Q is higher than 0.5. A Q greater than 0.5 indicates a lower rate of energy loss relative to the stored energy in the filter. At the output of these filter systems there will be a degree of ringing with input excitation. As the value of Q increases, it takes longer for the ringing to die out.

Figure 2 compares the low-pass filter responses of different Q values with respect to the frequency-domain and time-domain characteristics.

Figure 2: Impact of Q on the frequency response of low-pass filters (top) as well as the unit-step response (bottom) with a corner frequency of 1Hz

Figure 2: Impact of Q on the frequency response of low-pass filters (top) as well as the unit-step response (bottom) with a corner frequency of 1Hz

The top plot in Figure 2 shows the level of filter gain overshoot versus frequency for various Q values. The combination of this gain/frequency response, combined with the impact on the phase margins, results in the ringing (bottom plot) that you see in your filter’s output.

The most dramatic effect of higher Q values is the settling time, as seen in the bottom plot of Figure 2. The curve with a Q of 5 has considerable ringing compared to the Q with a curve of 0.707.

The two filter systems in Figure 3 have differing maximum Q values. The filter with a higher Q value demonstrates more ringing with a step stimulus at the input of the filter.

Figure 3: Comparing the step response of second- and sixth-order 0.5 Chebyshev low-pass filters

In Figure 3, the input signal for these filters is a 0.5V square wave. The maximum Q factor with the left-hand curve is 0.8547. The initial overshoot is approximately 0.15V above the final settling voltage value of 0.5V. This curve quickly settles to its final value with very little ringing.

The Q factor for Figure 3’s right-hand curve is equal to 6.513. The initial overshoot is approximately 0.23V overshoot. This curve, with a higher Q factor, takes a little longer to settle, with eight visible cycles. As you design filters using WEBENCH Filter Designer, you will find the maximum Q value for the particular filter you choose to design.

So how high can Q become before it causes problems? In our industry, the consensus is that Q should be less than 10. But, beyond that, assess the characteristics and requirements of your circuit. From there, you can decide what is the maximum acceptable Q for your system.

Additional resources

- Find out about TI’s OPA124 precision op amp.

- Begin designing today with the WEBENCH Filter Designer.

- “Q – Quality Factor Tutorial” from Radio-Electronics.com.

Timing is Everything: Design JESD204B clocking using system reference modes

Hello and welcome back to the “Timing is Everything” blog series. In a previous post, Timothy T. talked about the clocking requirements of the JESD204B interface standard that is gaining popularity for its ability to simplify design in high-speed data acquisition systems. In this post, I’m going to talk about the different system reference signal (SYSREF) modes of jitter synthesizers and cleaners, as well as how to use them to maximize the performance of your JESD204B clocking scheme.

The LMK04821 family of devices provide a good case study for this topic because they are high-performance, dual-loop jitter cleaners that can drive up to seven JESD204B converters or logic devices in a subclass-1 clocking scheme with device and SYSREF clocks. Figure 1 is a high level block diagram of a typical JESD204B system with the LMK04821 family devices as clocking solution.

Figure 1:Typical JEDEC JESD204B application block diagram

Figure 1:Typical JEDEC JESD204B application block diagram

The LMK04821 generates SYSREF signals with a single SYSREF clock divider from the voltage-controlled oscillator of the second phase-locked loop (PLL) . From the divider, the signal gets distributed to the individual output paths. Each output path contains digital and analog delays to adjust the SYSREF phase in relation to the device clock.

From the JESD204B standard, SYSREF can be in different modes, as shown in Figure 2. It can be a continuous (also known as periodic), gapped periodic or one-shot signal. The continuous and gapped-periodic SYSREF periods must be in an integer multiple of the local multiframe clock (LMFC) in order to avoid SYSREF pulses in the middle of a multiframe.

Continuous mode allows for continuous output. Many developers don’t use continuous mode due to crosstalk from SYSREF to the device clock. However, continuous mode enables the system developers to manually set up the correct deterministic-phase relationship between both signals. After the setup it can be changed to gapped-periodic SYSREF.

In gapped-periodic or one-shot modes, the output of the SYSREF clock divider is fed through a pulser to the output paths. The pulser gates the SYSREF signal and lets only a few pulses through. The pulse count can be set to one, two, four or eight pulses. Since there isn’t a periodic signal, the crosstalk from SYSREF to the device clock is minimized.

Another type of gapped-periodic SYSREF mode in the LMK0482x is the request mode, which outputs a continuous stream of SYSREF pulses as long as the SYNC/SYSREF_REQ pin is high.

Figure 2:The SYSREF modes of the LMK0482x are a) continuous SYSREF, b) pulsed SYSREF (one-shot or gapped periodic), c) and SYSREF request (gapped periodic)

In LMK04821 devices, the internal SYSREF distribution path is shared with the output-divider synchronization path. Therefore, it needs a specific register write sequence to enable synchronized outputs and glitch-free SYSREF pulse generation. In Table 1, the methods I’ve described are listed with their register write sequences. Table 1 also shows the internal-register field names with content as a decimal value. Steps with the same number are interchangeable.

Table 1:Register write sequences to enable different SYSREF modes

The JESD204B standard is reducing the layout efforts while introducing serialized data transmission between signal converters and logic devices. By taking full advantage of the SYSREF modes of your JESD204B-enabled clock device, you can easily create deterministic phase relationships in the whole system.

Are there other clock design challenges you’d like us to cover regarding JESD204B designs or others? Let me know by logging in to post a comment below.

Additional resources

- Read the blog series about JESD204B subclasses.

- Read this blog post about JESD204B subclass-1 clocking timing requirements.

- Read Thomas Neu’s white paper, “Ready to make the jump to JESD204B?”

- Read this Analog Applications Journal article, “When is the JESD204B interface the right choice?”

- Get useful design tips on various clock and timing design challenges from the “Timing is Everything” blog series.

Inductive sensing: How far can I sense?

In my last few blog posts on inductive sensing, I introduced the latest addition to TI’s inductance-to-digital converter (LDC) portfolio: the multichannel LDC1612, LDC1614, LDC1312 and LDC1314. The LDC1312 and LDC1314 are 13.3KSPS 12-bit resolution converters, useful for a wide range of applications such as rotational knobs, keypads or flow meters. If system-boundary conditions allow, they can be configured in 16-bit mode without sacrificing the sampling rate. The dual-channel LDC1612 and quad-channel LDC1614 have integrated 28-bit data converters for use in very high-precision applications such as linear encoders or strain gauges.

How improved resolution increases sensing distance

The size of the magnetic field lines around a coil are proportional to the diameter of the sensor inductor. Therefore, the maximum sensing distance of the LDCs is a function of the coil diameter. The resolution and signal-to-noise ratio of the LDC do play a role, however, in determining how far a conductive object can be from the coil in order to detect its presence or measure its distance.

Using a 28-bit LDC over a 12-/16-bit LDC has two advantages:

- You can determine target position to higher accuracy.

- You can detect targets at longer distances.

Methodology and results

To determine the maximum target distance that the new multichannel LDCs can sense, I stepped an aluminum target in 0.1mm increments axially from the 14-mm diameter sensor coil of the LDC1612 evaluation module and captured the LDC response. I recorded both the code change between steps (Figure 1) and the standard deviation of 100 samples per step (Figure 2).

Figure 1: Code change for 0.1mm steps versus target distance

Figure 2: Standard deviation versus target distance, 100 samples per step

Next, I used the measurement data on resolution and standard deviation to determine the maximum target sensing distance for the following conditions:

- The output code step size sufficient to resolve 0.1mm steps.

- The noise floor at the given target position is low enough to determine its position with 6σ probability (99.99966%).

By examining the data, I identified the distance above which these two conditions no longer hold true.This point is the maximum target distance that still meets my accuracy requirements above. The maximum target distance in each case is shown in Figure 3.

Figure 3: Maximum target distance for resolving 0.1mm steps with 6σ probability

Guidelines for setting your target distance

The maximum target distance that you can sense varies with system parameters such as accuracy requirements and target material composition. Therefore, your application may have a longer or shorter maximum sensing range. However, since sensing range scales with coil diameter, it is possible to establish some rules of thumb from the data:

- LDCs such as the LDC1312 and LDC1314 operate best if the maximum target distance is kept within half of a coil diameter.

- In contrast, the high resolution of the channel LDC1612 and LDC1614 can be used to effectively sense targets as far as two coil diameters away from the sensor.

In my next post, I’ll explain how to configure the LDC1312 in 16-bit mode, which is beneficial in medium-resolution applications in which the faster sampling rates of the LDC1312 are preferable to the LDC1612.

Additional resources

- Learn more about inductive sensing.

- Read more blog posts about designing with LDCs.

- Check out this TI Design reference design and video for a 1-degree dial using the LDC1314.

- See how LDCs work in this Touch on Metal Buttons with Integrated Haptic Feedback reference design.

- Start a design today with WEBENCH® Inductive Sensing Designer.

Managing input data rates is a breeze

In my previous post, I talked about why you might want to use Radio frequency (RF) sampling data converters to handle higher bandwidths in a design. Data converters that operate directly in the RF bands without the additional circuitry of mixers and local oscillators are very alluring. Plus, it’s possible to sample at 4GSPS and beyond.

But wait! How can you transfer digital data to the field-programmable gate array (FPGA) or processor at those speeds? A traditional low-voltage differential signaling (LVDS) or complementary metal-oxide semiconductor (CMOS) interface is not capable of operating that fast. A JESD204B serialized interface is more common; however, a 12-bit converter sampling at 4GHz within the interface could require 80Gbps of data across the channel. This is no small feat. It requires a combination of high-speed serializer/deserializer (SERDES) transceivers and a large number of lanes. This taxes the capability, power constraints and size of the device.

But it is possible to reduce the input data rate by decimation. Decimation is a simple technique where you eliminate sample points from the data stream to reduce the data rate. Figure 1 illustrates a decimate-by-2 operation. Does this technique distort the waveform and lose information? Not exactly. The information is still intact; the drawback is that the decimation operation creates additional images. A decimate-by-2 will introduce images centered at half the sampling-rate point (Fs/2). The decimation process is accompanied by a digital filter to eliminate these images.

A decimate-by-2 function is equivalent to a data converter operating at half rate, with an analog antialiasing filter operating at half the bandwidth. You can also cascade multiple decimate-by-2 stages together to reduce the input data rate to the desirable level.

Figure 1: Decimation in the time domain and frequency domain

So what’s the penalty for this approach? The reduction in data rate will limit the system’s bandwidth capability. Shannon’s sampling theorem still applies. If a 4GSPS device is decimated by 8, for example, the resulting input data rate would be 500MHz, which can support a signal bandwidth of 250MHz.

Another useful digital feature is a numerically controlled oscillator (NCO). An NCO is a programmable oscillator that can digitally move the signal captured to a digital baseband location. A common approach is to capture the signal in the RF band and use the NCO to move the signal to zero IF (ZIF). Figure 2 illustrates this approach. The signal can be located at any arbitrary RF frequency and moved down to a known location. Once centered at 0Hz, the maximum data rate required is contingent only on the signal bandwidth. The rule of thumb is to select the output sampling rate based on your RF frequency of operation and to select the input data rate based on the maximum signal bandwidth.

Figure 2: Example of an NCO downconverting operation

The ADC12J4000 RF sampling analog-to-digital converter operates at a sampling rate of 4GSPS. This device uses the JESD204B serialized data interface. It includes decimation modes up to 32x and also has an NCO. Engaging the decimation and NCO allows you to keep the maximum output sampling rate while reducing the input rate based on signal-bandwidth requirements or the processor’s serialization speed limitation.

Come back next month, when I’ll discuss how data-converter aliasing can be your friend.

Additional resources

- View a video on How to sample and decimate frequencies with ADC12J4000.

- Learn more about the JESD204B interface for high-speed analog-to-digital converters (ADCs).

- See all posts in RJ Hopper’s RF sampling blog series.

Inductive sensing: Improve the ENOB of a multichannel LDC by 4 bits in 3 simple steps

In a recent inductive sensing blog post, I introduced the new new multichannel LDCs: the 12-bit LDC1312 and LDC1314 and the 28-bit LDC1612 and LDC1614.

There are scenarios in which you might want to use the 12-bit LDC1312 or LDC1314 due to higher sample rates or lower cost, when the resolution of the 12-bit LDC isn’t quite high enough for your particular system needs, for example in this 1-degree dial. In this case, you can use the gain and offset registers to improve the effective number of bits (ENOB) by up to 4 bits. Measurement timing is unaffected by using gain and offset.

The gain/offset feature works because the LDC1312 and LDC1314 have an internal 16-bit data converter, but they only display 12 of those bits in the data registers: DATA_CH0, DATA_CH1, DATA_CH2 and DATA_CH3. By default, the gain feature is disabled and the DATA registers display the 12 most significant bits (MSBs) of the 16-bit word. However, it is possible to shift the data output; see Figure 1.

Figure 1: Conversion data output gain

Employing the gain of 4x, 8x or 16x causes a 2-bit, 3-bit or 4-bit data shift, which is equivalent to increasing the maximum effective number of bits by 2 bits, 3 bits or 4 bits, respectively.

Let’s use a simple example to illustrate how gain and offset work. The example uses an LDC1314 evaluation module. My target is a U.S. quarter that moves between a 0.2mm target distance and an infinite target distance.

Here’s how to optimize the resolution in three simple steps:

- Determine system boundaries. When moving the quarter between the minimum target distance (0.2mm) and maximum target distance (infinite), I measure the following (Table 1):

Table 1: ENOB before applying gain

Using the gain feature discards the MSBs; therefore, it’s important to ensure that the maximum output scale does not go below zero or above the full scale of the new data output. The datasheet shows that the maximum output range must be:

- ≤ 100% of full scale with gain = 1x

- ≤ 25% of full scale with gain = 4x

- ≤ 12.5% of full scale with gain = 8x

- ≤ 6.25% of full scale with gain = 16x

2. Apply gain. The full-scale data word is 212-1 = 4,095. My example shows a delta of 90 codes between the minimum and maximum target positions, which is only 2.2% of full scale. I can therefore comfortably use the maximum gain setting of 16x. Under this condition, I measure the following (Table 2):

((*) signal is clipped

Table 2: ENOB after applying gain

My code delta has improved greatly, but the data output at the minimum target distance clips at the full scale of my new data word.

3. Subtract offset. While my system only uses 2.2% of full scale, it crosses the full-scale boundary, which results in a loss of information. To fix this issue, I can use the offset register to subtract a fixed offset from the data output. The maximum target distance output code is 3,212, so I can easily subtract 2,000 codes.

(*) signal is clipped

Table 3: ENOB after applying gain and offset

With a gain of 16x and an offset of -2,000 codes, the LDC now records data between 1,212 and 2,670, as shown in Table 3. This is well within the output-code limits of 0 to 4,095. The code delta is 1,458 codes, which is a 4-bit improvement over the default case with a gain of 1.

Figure 2 shows the operating output range for this example without gain, with a gain of 16, and with a gain of 16 and an offset of -2,000.

Figure 2: Conversion signal range increases after applying gain and offset

What if the resolution is still insufficient?

In this simple example, the effective resolution improved by 4 bits (from 6.5 bits to 10.5 bits) without any impact on timing or power consumption. If this effective resolution is still insufficient for your system, consider using one of our 28-bit multichannel devices, the LDC1612 or LDC1614.You can read more about the resolution benefits of the the LDC1612 and LDC1614here.

Leave a note below and let me know future topics you’d like for me to discuss about multichannel LDCs.

Additional resources

- Learn more about inductive sensing.

- Read more blog posts about designing with LDCs.

- Watch the EVM quick-start video and start designing with your LDC1312 evaluation module.

- Check out this TI Design reference design for a 16-button keypad using the LDC1314.

- Start a design today with WEBENCH® Inductive Sensing Designer.

What are you sensing? A novel approach for capacitive-based liquid-level sensing

Various methods have been used to determine the liquid-level height in containers, but recently, capacitive sensing has become popular due to the accuracy and resolution of the measurements. If you have designed with capacitive-based liquid-level sensing, you may have experienced false measurement readings when you move your hand closer to your system. This is caused by the conventional capacitive technique’s limitations with robustness, especially with any external parasitic capacitance interference such as a human hand. As an example, think of a coffee maker that uses liquid level sensing to determine the amount of water required for each cup of coffee. To make the perfect cup, you need the right amount of water. If a person interacts with the coffee maker while it is running, the parasitic capacitance interference from the human body will disrupt the coffee mixture.

In this post, I’ll talk about the conventional method of liquid-level sensing, and a novel approach TI has come up with a called the out-of-phase (OoP) technique, employing the FDC1004 capacitance-to-digital converter. It provides the necessary barrier to minimize any interference, while maximizing the signal-to-noise ratio and overall robustness of the system.

Figure 1 shows the typical liquid-level sensing application setup.

Figure 1: Liquid-level sensing setup

The conventional method

The conventional method uses the parallel fingers topology: one electrode driven with the excitation signal and a second electrode connected to ground (GND), as shown on the left in Figure 2. The issue with a GND-referenced electrode is that the water has a voltage potential difference. When the hand approaches the container with the liquid, an additional parasitic capacitance is introduced into the model and the self-body capacitance directly couples to the potential difference of the water. This results in false-measurement deviations and system inaccuracy.

Figure 2: Conventional method versus OoP method

The OoP technique

The OoP technique relies on a symmetrical sensor layout, and also uses the shield drivers on the FDC1004 capacitance-to-digital converter in a unique way to counteract the effects of human-body capacitance and stabilize measurements. With the OoP technique, the liquid potential is kept constant during the excitation/drive phases by using a differential capacitive measurement, thus eliminating human-body capacitance effects from the measurements. Instead of using a GND electrode, the CINx electrode is paired with a SHLDy electrode. CINx and SHLDy have the same waveform but are 180 degrees out of phase; this is possible by setting the FDC1004 in a differential-mode configuration.

I collected hand-interference capacitance measurements with the capacitive-based liquid-level sensing TI Design reference design and compared it to the conventional method with electrodes the same size. Figure 3 shows the test setup, with the reference design on a container and connected to the FDC1004 evaluation module (EVM). Table 1 shows the capacitance measurements at a water-level height of 5cm, with the human hand a fixed distance away from the front of the container. When the hand is directly touching the container (a 0cm hand distance), the conventional method has a change in capacitance from the baseline reading (no hand present in the system) 20 times larger than the OoP technique. The calculated level absolute error dropped from about 9% to about 0.4% with the OoP technique. Over the full range of the system (0-8cm level heights), the overall absolute error of the OoP technique is about 0.5%.

Figure 3: Test setup with the capacitive-based liquid-level sensing TI Design reference design

Table 1: OoP and conventional liquid-level technique comparison

Robustness with any capacitive-based liquid-level sensing system is important for reliability and accuracy. The OoP technique mitigates the effect of any external parasitic capacitance compared to the conventional method. A sensor layout that is as symmetrical as possible will maximize the performance of the technique.

Additional resources

- Learn more about capacitive sensing.

- Check out the Capacitive Sensing: Out-of-Phase Liquid Level Technique application note.

- Get started with TI’s “Capacitive-based liquid-level sensing” TI Design reference design.

- Start your design today with the FDC1004 EVM.

- Read more blog posts about capacitive sensing design.

- Search for answers and get help with your designs in the TI E2E™ Community Capacitive Sensing forum.

Two parameters to consider when selecting ESD protection diodes for HDMI 2.0

I was walking around the television section of my local electronics retailer when I noticed that the majority of the televisions had 4k resolution. I also noticed that my favorite fictional political drama show was available in 4k streaming. If my shopping experience alone is a good gauge, it seems that 4k content and the devices to support it are proliferating in the market.

To support all this 4k content, the newest HDMI standard, HDMI 2.0, was introduced in September 2013 by the HDMI Forum. It has many advantages over HDMI 1.4, but it also adds circuit protection design challenges.

The differences between HDMI 2.0 and HDMI 1.4

Both standards support the same connector, so what benefits does HDMI 2.0 bring to consumers?

- 4k resolution at 50/60 frames per second (fps) versus HDMI 1.4’s 4k resolution at 24fps.

- Up to 32 audio channels (for a multidimensional, immersive audio experience).

- Dual video screens simultaneously displayed to the same screen in 1080p.

- Simultaneous delivery of multistream audio to as many as four users.

- Support for wide-angle 21:9 video aspect ratio.

- Dynamic synchronization of video and audio streams.

- Consumer electronic control (CEC) 2.0 provides expanded command and control of consumer electronics devices through a single remote.

The introduction of these additional features has bumped the overall data rate of HDMI 2.0 up to 18Gbps from 10Gbps in HDMI 1.4. This increase in data rate is great for adding additional features for the consumer, but it presents challenges when selecting the appropriate electrostatic discharge (ESD) protection diode during circuit protection design.

Key parameters for selecting ESD protection diodes for HDMI 2.0 include:

- Parasitic capacitance. In HDMI 2.0, high-speed transition-minimized differential signaling (TMDS) lines show the increases in data rate. TMDS lines for HDMI 2.0 have a maximum data rate of 6Gbps versus 3.4Gbps in HDMI 1.4. Parasitic capacitance becomes one of the most important parameters in selecting an ESD protection diode to ensure the signal integrity of TMDS lines.

When selecting an ESD protection diode for HDMI 2.0, always consider the input/output (I/O) capacitance of the diode first. Make sure that the diode’s capacitance fits into the capacitance budget allowed for TMDS lines. When selecting, look for an I/O capacitance of less than 0.5pF.

Also consult the eye diagram included in the data sheet. This will give you a good indication of the performance of the ESD device in an HDMI 2.0 system. Figure 1 is an example eye diagram.

Figure 1: HDMI 2.0 test point 1 (TP1) eye diagram of TPD4E05U06 ESD protection device

2. Clamping voltage and RDYN. Lower capacitance is not the only parameter to consider when selecting an ESD protection diode for HDMI. With system processors moving to lower voltage nodes, there is an increased risk of failure from electrical overstress (EOS) during an ESD strike. When considering an ESD protection diode, always look at the clamping voltage and RDYN of the device.

The clamping voltage is the voltage that the ESD diode clamps to during an ESD strike. This is one of the most important parameters for ESD protection device because it is what voltage the system side of the connector will see during an ESD strike.

The datasheet lists different ways to specify the clamping voltage of an ESD device. Some devices will specify clamping voltage by using a transmission-line pulse (TLP) test. Current levels for the TLP test can range from 1A to 16A. Others specify the clamping voltage at 30ns during an 8kV IEC 61000-4-2 contact test. With all of these different ways to define clamping voltage, it can be confusing when comparing ESD protection diodes.

Figure 2: Current versus voltage curve for a transient voltage suppression (TVS) diode

One general rule of thumb when selecting ESD protection diodes is the lower the RDYN, the lower the clamping voltage. The dynamic resistance is the effective resistance of the diode’s path to ground during an ESD strike. Shown in Equation 1, RDYN is proportionally related to the clamping voltage. It is also represented as the slope of the diode’s I-V curve in Figure 2. There are other factors such as breakdown voltage and parasitic capacitance. Nevertheless, lower dynamic resistance leads to better clamping-voltage performance for the diode.

When selecting ESD protection diodes for HDMI 2.0 designs, look for two main things: capacitance and RDYN. Low parasitic capacitance will ensure that that the design will be able to preserve the HDMI 2.0 signal integrity. Low RDYN to ensure a low clamping voltage during an ESD strike. Consider these parameters to keep the system safe and the 4k content rolling.

Additional resources

- Check out TI’s High-Definition Multimedia Interface (HDMI) ESD protection products.

- Download these documents for more information about ESD protection:

How to optimize differential amplifier noise

Signal gain and noise gain are both important to amplifier circuit design. Signal gain is obviously important because you want to have accurate control of your signal amplitude. Noise gain is also important, even though it does not directly impact signal amplitude, because it impacts amplifier stability and loop gain, both of which have an impact on signal quality. Thus, it’s important to be able to calculate both noise gain and signal gain for a particular circuit. Once you have these numbers, you can use the datasheet guidelines to optimize your circuit.

Let’s quickly review signal gain with fully differential amplifiers, both inputs are inverting inputs; there is no noninverting input, so your signal gain is When you build the board, you physically solder RF onto the board, so you know the value of RF – or do you? Depending on the particular amplifier and board design, you may need to consider extra resistance. TI’s LMH5401 fully differential amplifier has an extra 25Ω on chip between the amplifier output and the feedback connection pins on the amplifier package. Because this amplifier is only 3mm by 3mm, and because the feedback connection pins are directly adjacent to the amplifier input pins, any measurable board resistance is not likely. You should, however, consider any board traces longer than 1cm possible sources of extra resistance. So if you’re using the LMH5401, you’ll need to add onboard feedback resistance to the on-chip resistance.

When you build the board, you physically solder RF onto the board, so you know the value of RF – or do you? Depending on the particular amplifier and board design, you may need to consider extra resistance. TI’s LMH5401 fully differential amplifier has an extra 25Ω on chip between the amplifier output and the feedback connection pins on the amplifier package. Because this amplifier is only 3mm by 3mm, and because the feedback connection pins are directly adjacent to the amplifier input pins, any measurable board resistance is not likely. You should, however, consider any board traces longer than 1cm possible sources of extra resistance. So if you’re using the LMH5401, you’ll need to add onboard feedback resistance to the on-chip resistance.

or -1.6 dB, which does match the TINA-TI simulation.

or -1.6 dB, which does match the TINA-TI simulation. Thus, this circuit is not stable according to the datasheet. Note that the resistive loss on the output resistors is not included in noise gain, even though they do contribute to loss in the signal path.

Thus, this circuit is not stable according to the datasheet. Note that the resistive loss on the output resistors is not included in noise gain, even though they do contribute to loss in the signal path. While Figure 4 has only one more component, it is easier to calculate the noise gain if you imagine that R6 is two resistors of 50Ω each, connected to an ideal (noiseless) voltage source of 0V. In this case, half of R6 is in parallel with RG, so the noise gain is now

While Figure 4 has only one more component, it is easier to calculate the noise gain if you imagine that R6 is two resistors of 50Ω each, connected to an ideal (noiseless) voltage source of 0V. In this case, half of R6 is in parallel with RG, so the noise gain is now - Download the LMH5401 datasheet.

- See TI's entire high-speed amplifier portfolio.

- Explore all of our fully differential amplifiers.

- Check out my other high-speed amplifier blog posts.

How to get started with current sense amplifiers – part 3

In parts one and two of this series, I discussed concepts related to specifications of current-sense amplifiers and how to use the application requirements to narrow device selection. In this installment, I’ll discuss how the current range helps derive the shunt-resistor value, as well as how the current range and shunt value combined with device performance drive a trade-off between accuracy and power dissipation.

Until the recent release of TI’s INA250 current-sense amplifier (more on this later), the current didn’t actually pass through the current-sense amplifier. Therefore, the current range being measured didn’t directly dictate the device specifications.

For an analog output current-sense amplifier, the maximum current range combined with the full-scale input (maximum differential input voltage) will derive the ideal shunt resistor value, as shown in Equation 1:

If you look at most current-shunt monitor data sheets, you’ll notice that the maximum differential voltage isn’t specified; rather, a maximum output voltage swing is specified. You’ll want to match this to the full-scale input range of the next link in the signal chain. To maximize performance, you’ll want the maximum-output voltage swing to be greater than the next link’s full-scale input range. Typically, the maximum output swing is a function of the supply voltage supplied to the current-sense amplifier. For example, with the INA282, the output-swing range is defined as 0.4V below the supply voltage to 0.04V above the voltage on the ground pin, as shown on page 6 of the datasheet (Table 1).

Table 1: Electrical characteristics of the INA82 current-sense amplifier

If you use the full-scale input range as the desired output swing of the current-shunt amplifier with maximum current flow, then you can modify the shunt-resistor equation, taking into account the gain (GAMP) of the current-sense amplifier. Equation 2 shows this modification.

Let’s look at two examples of how to use this equation. For both examples, we will use the maximum current as 5A and the full-scale input of the next link in the signal chain as 2.5V. Let’s consider using either the INA286 (gain of 100V/V) or INA284 (gain of 500V/V), as shown in Table 2.

Table 2: INA286 and INA284 gain and ideal RSHUNT value with a maximum current of 5A and a full-scale input of 2.5V

The ideal RSHUNT value may not be readily available, so you may have to choose the closest value – which may be is less than ideal. The reason you need to choose a resistor that is of a lesser ohmic value than the ideal is to keep the voltage input to the next link below the full-scale input level.

Using Equation 3, you will also need to verify that the minimum current value creates an output voltage from the current-shunt amplifier that is above the minimum output voltage.

Looking back at these two examples, you can calculate the minimum current for each solution as 80mA.

The next question is what to do with the fact that I have just calculated multiple options for different combinations of shunt value and amplifier gain. The answer comes down to a trade-off between the desired accuracy of the application versus the power dissipated in the shunt resistor. While I have not delved into accuracy yet, I will cover this in part 4 of this series; briefly, the larger the value of RSHUNT, the higher the accuracy. However, as shown in Figure 3, the higher values of RSHUNT lead to an increase in the power dissipated by the shunt resistor and adds to the overall load of the system.

Table 3: INA286 and INA284 power dissipation and voltage error

You’ll need to look at various current-sense amplifier options for gain and offset voltage and calculate how those options combined with the current range will affect the shunt-resistor value, achievable accuracy and power dissipation.

Most digital-output devices, such as the INA226, specify a full-scale shunt-voltage input range. This simplifies the calculations in many cases because there is not an additional gain stage to trade off against. The shunt value is simply the closest-available value resistor found by dividing the device’s maximum-input voltage by the maximum current.

I mentioned briefly the brand-new INA250 current-sense amplifier. By integrating the shunt resistor, the INA250 can support a maximum current level based on the heat generated by the current flowing through the shunt. Look for more information in future blog posts about how the INA250 is redefining precision current measurement.

In the next installment, I will address the basics of accuracy and how device selection affects accuracy.

Additional resources

- Learn more about TI’s broad current-sense portfolio.

- Watch this video about how the INA300 is optimizing overcurrent detection.

- Learn from online training about getting started with current-sense amplifiers.

- Check out these related TI Designs reference designs:

How USB Type-C helps make cars as smart as phones

Most of us have become so attached to our phones to stay connected with work, family and friends. However, the place where I feel most unconnected is in my car. My phone is in the passenger seat, gathering new texts, emails, missed calls and social media notifications. At a stoplight, I often grab it to quickly check new notifications. But when I arrive at my destination my phone’s battery is typically low.

I tried all the Bluetooth® products and the 12V phone chargers. I get excited for a while when I buy a new one, but it quickly fails to meet my demands. People complain about my voice quality when I use the speaker in my car, and my phone (which is nearly as capable as a laptop) barely maintains a charge, never coming close to charging with the 500mA current. Not to mention, the audio content is not getting to the car to share on its many capable displays.

When I work with Universal Serial Bus (USB) Type-C, however, I get so excited about how it could change my driving experience that I am actually holding off on trading in my current vehicle until someone realizes the full potential of USB Type-C in cars. USB Type-C would easily provide 15W of charging power (as much as 100W with USB Power Delivery) and 20Gbps of data; even my phone would have to work hard to fill that pipe. It makes my electronics-loving heart excited. I might have to upgrade my phone (or at least its memory); just please don’t tell my wife. On the other hand, please do tell her because this capability would enable all passengers to enjoy their phones’ great capability even more when traveling in my car. It would be even easier to share social media posts with the entire family.

The TUSB320, a device that provides USB Type-C configuration channel logic and port control, could enable this experience and is available today. The device handles all of the USB Type-C channel controller (CC) and mode configuration communication for USB 2.0.

Figure 1: USB 2.0 implementation of Type C

The new TUSB321 can work with the HD3SS3212 device to enable a full USB 3.1 solution, thus using the full data transfer benefits of the USB Type-C connector.

Figure 2: USB 3.0 implementation of Type C

TUSB320, TUSB321, HD3SS3212 and HD3SS460 are commercially available and Q100 qualification is possible on most devices. It’s so exciting to think that my next car might have these capabilities.

Are you ready to utilize your phone capability while in the car and arrive with a full charge? USB Type-C can make this a reality in your next vehicle. If you have any questions about how TI products are bringing this experience to life, please leave a comment below.

Inductive sensing: How to sense spring compression

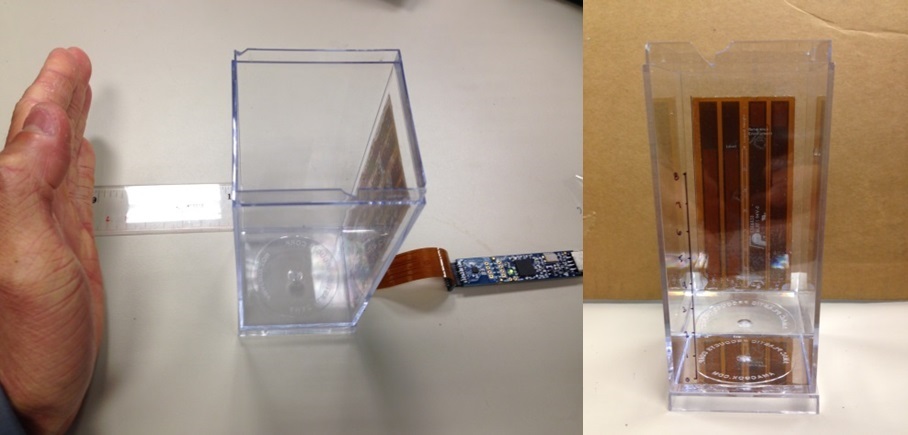

While most inductive-sensing applications use either printed circuit board (PCB) coils or wire-wound inductors as the sensor, inductance-to-digital converters (LDCs) can use almost any inductor as a sensor – even a spring. Springs are useful as sensors because the spring’s inductance varies directly with changes in length or other physical changes. Figure 1 shows how to connect a spring to an LDC.

Figure 1: Spring used as a sensor by an LDC

To evaluate using a spring as a sensor, I used the LDC1612EVM evaluation module to measure the inductance of a spring as I extended the spring across a range of lengths. To do this, I first removed the on-board sensor from the EVM and replaced it with a spring. The spring was made of 0.7mm-thick steel, had 46 turns and a diameter of 7.3mm. Figure 2 shows the spring that I connected to the EVM.

Figure 2: Spring setup

The inductance of my spring is too low to be used as a sensor for the LDC1612 on its own, so I added a 2.2μH fixed wire-wound surface-mount device (SMD) inductor in series. (For details on how to use a series inductor to increase sensor impedance, see my blog post “How to use a tiny 2mm PCB inductor as a sensor.”) With a 1nF sensor capacitor, the oscillation frequency was 2.5MHz. Figure 3 shows the sensor components that I used.

Figure 3: Sensor components

I stretched the spring from 50mm to 100mm in 5mm increments and measured LDC1612 output data at each step. From the data, I calculated the sensor inductance using Equation 1:

where

and fref = reference clock (40MHz on the LDC1612 EVM).

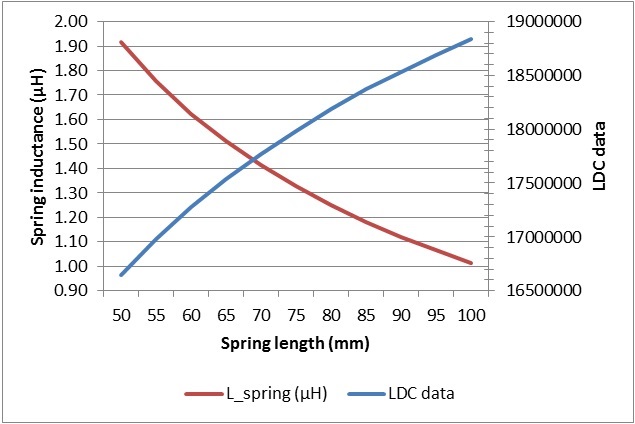

Figure 4 shows the data and spring inductance after subtracting the 2.2μH series inductor.

Figure 4: LDC1612 data and spring inductance versus spring length

The data samples that I collected when extending the spring from 50mm to 100mm in 5mm steps are monotonic and can be used to precisely determine the length of the spring. During this spring-compression range, the inductance decreases from 1.92μH (LDC output 16,644,000) to 1.01μH (LDC output 18,840,000). Thus, over this range, stretching the spring by 1μm results in a 44-codes increment in the LDC1612 data output on average.

This data shows that you can use inductive sensing to directly measure the inductance shift that results from compressing a spring, and that springs can serve as an alternative sensor to PCB coils and wire-wound inductors.

Additional resources

- Learn more about inductive sensing.

- Download the LDC1612 datasheet.

- Read more inductive sensing blogs, including “How to use a tiny 2mm PCB inductor as a sensor.”

- Check out WEBENCH® Inductive Sensing Designer.

- Search for answers and get help with your designs in the Inductive Sensing forum of the TI E2E™ Community.

Three things you should know about Ethernet PHY

The evolution of Ethernet is fascinating. More than 40 years ago, Robert Metcalfe was asked to create a local area network (LAN) for the storied Palo Alto Research Center. The result of Metcalfe’s innovative work would be standardized as Ethernet – an adaptive technology that would forever revolutionize the world of communications. Fast-forward to modern society, and Ethernet is everywhere.

What is Ethernet?

Today, many people think that Ethernet means the Internet. While these two concepts are indeed related, Ethernet is simply an interface specification (IEEE 802.3) comprising many subsections and specifications defining the physical and data-link layers of the Open Systems Interconnection (OSI) model. One of the most important pieces that came out of IEEE 802.3 is the Ethernet physical layer transistor (PHY).

Figure 1 shows an example block diagram of how data is transferred to and from a standard RJ45 Ethernet cable to a processor.

Figure 1: Ethernet PHY system block diagram

These are the three things you should know about Ethernet PHY:

- It is a transceiver that is a bridge between the digital world – including processors, field-programmable gate arrays (FPGAs) and application-specific integrated circuits (ASICs) – and the analog world. An Ethernet PHY is designed to provide error-free transmission over a variety of media to reach distances that exceed 100m.

- The Ethernet PHY is connected to a media access controller (MAC). The MAC is usually integrated into a processor, FPGA or ASIC and controls the data-link-layer portion of the OSI model. The media-independent interface (MII) defines the interface between the MAC and the PHY. Variations of the MII are available that provide minimal pin count and varied data rates depending on system requirements.

- Speed matters. There are many different variants of the Ethernet standard, with corresponding PHYs, that range from 1Mbps to 100Gbps. The majority of Ethernet applications use a 10/100Mbps (see TI’s DP83848) or 10/100/1000Mbps PHY. The physical mediums that carry the data to the Ethernet PHY include twisted pairs, CAT5, coaxial cables, backplanes and fiber optics.

Without Ethernet, you would not be able to quickly send data from one point to another. Forty years after its creation, Ethernet has become truly indispensable. What else would you like to know about Ethernet PHY? Leave a comment below. Watch next month for a blog post on how Ethernet technology is shifting new modern markets.

Additional resources

- Find out more about TI’sDP83848 single-port 10/100Mbps Ethernet PHY.

- Learn about TI’s Ethernet portfolio.

- Check out this electromagnetic interference (EMI)/electromagnetic compatibility (EMC)-compliant industrial temp dual-port Gigabit Ethernet TI Design reference design.

How to get started with current sense amplifiers – part 4

In previous installments of this series, I discussed implementation alternatives and how those decisions affect and are affected by device parameters. In this post, I’ll explain how device parameters as well as system factors can affect the achievable accuracy.

To understand how accurate a measurement we can achieve, we first need to understand the sources of potential errors. Here is a list of two types of error sources – note that this is not an exhaustive list, but rather highlights some of the main sources:

Amplifier-related error (noise) sources:

- Input offset voltage (VOS).

- VOS drift.

- Common-mode rejection ratio (CMRR).

- Power-supply rejection ratio (PSRR).

- Gain error.

- Gain-error drift.

Nonamplifier error sources:

- Printed circuit board (PCB) layout.

- Shunt-resistor tolerance and drift.

- Gain-setting passives tolerance, matching and drift.

The worst-case accuracy is a simple linear summation of all error sources, e, shown in Equation 1:

It is statistically improbable that all errors are maxed at the same time, so a more probable accuracy equation would be a root-sum-square of the error sources, shown in Equation 2:

First, let’s consider the external error sources. The VSENSE that the amplifier sees is what is across the input pins, which will be different than what a designer may experience if measuring across the resistor. Ideally VSHUNT = VSENSE, but parasitics and trace etch will cause this not to be true. A Kelvin connection will minimize the PCB parasitic-error contribution.

When it comes to shunt-resistor tolerance and drift, there will be a trade-off between the cost you are willing to pay and the required performance for the application. The shunt-resistor temperature drift is one of the main error sources over temperature, unless you choose a costly resistor. High-precision (0.1%), low-drift (50ppm/°C) resistors on catalog distribution sites cost somewhere between US$4.00 and US$8.00 in 1,000-unit quantities.

The error contribution of an operational amplifier’s external circuitry is eliminated using a current-shunt monitor due to its integrated, matched, low-drift gain-resistor networks. The effects of these on-chip networks are factored into the error contributions of the current-sense amplifier itself.

When it comes to amplifier error sources, you will need to make similar trade-offs on precision versus cost. It is important to review the operating conditions of each of the parametric specifications listed in the datasheet and compare those to your actual operating conditions. For this discussion, I will focus on two of the main error contributors: input offset voltage and gain error.

The input offset voltage will be the dominant error source at low VSENSE levels. If you simplify and assume that VSENSE = VSHUNT = ILOAD x RSHUNT (no parasitic error contribution), then the error contribution of VOS is calculable using Equation 3:

Let’s look at two different current-shunt monitors, the INA199 and INA210, to see how VOS will affect the error. The INA199 datasheet lists the VOS(MAX) as 150µV, while the INA210 is 35µV. Table 1 shows the respective error contributions using a current value of 1mA and a 1Ω shunt resistor.

INA199 | ||

VOS(MAX) | 150µV | 35µV |

VOS error | 15.0% | 3.5% |

Table 1: INA199 and INA210 current-shunt monitor error contributions

If you are measuring low current values that will result in low VSENSE values, it is critical to minimize VOS to minimize the error. As VSENSE grows relative to VOS(MAX), this error contribution is minimized. If VSENSE is 1,000 times the value of VOS, then the error contribution is 0.1%. On the other end of the spectrum is when VSENSE is much greater than VO. The main error contribution will be the gain error. In most datasheets, this is specified as a flat percentage, and the contribution is a straightforward percentage adder.

Let’s see how these two errors contribute to a total error, again assuming that they are the only two error sources. Figure 1 shows how the linear sum as well as the root-sum-square method of error calculation work for the INA199 and INA210.

Figure 1: INA210 and INA199 total error

Here, the offset voltage is the major error source when VSENSE is low, and gain error dominates when VSENSE is high relative to VOS.

My analysis has simplified the error calculations to two primary sources. However, current measurement accuracy is a very complex subject with many moving parts that need to be traded off against each other to maximize performance under specific operating conditions. One of the key elements for a more thorough analysis is temperature. The temperature drift will affect multiple specifications, including shunt-resistor value, offset voltage and gain error. Using a current-shunt monitor that has zero drift, including the INA210 or INA282, will help minimize the offset drift contribution.

Additional resources

- Read the datasheets for the INA210, INA199 and INA282 current-shunt monitors.

- Read this “Current sensing tutorial” article series on EE Times.

- Watch our training series on current-sense amplifiers.

- Check out related TI Designs reference designs: